多层pcb打样过程中电镀夹膜产生的原因和如何改善处理

- 发表时间:2021-12-25 11:42:34

- 作者:小编

- 来源:诚暄PCB

- 人气: 本文有568个文字,预计阅读时间2分钟

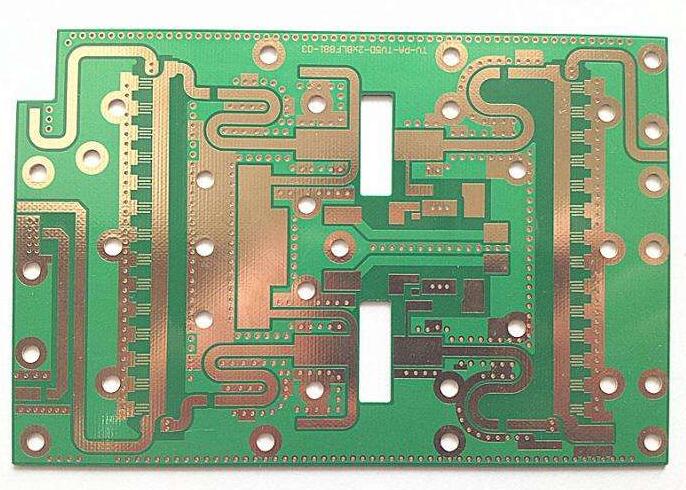

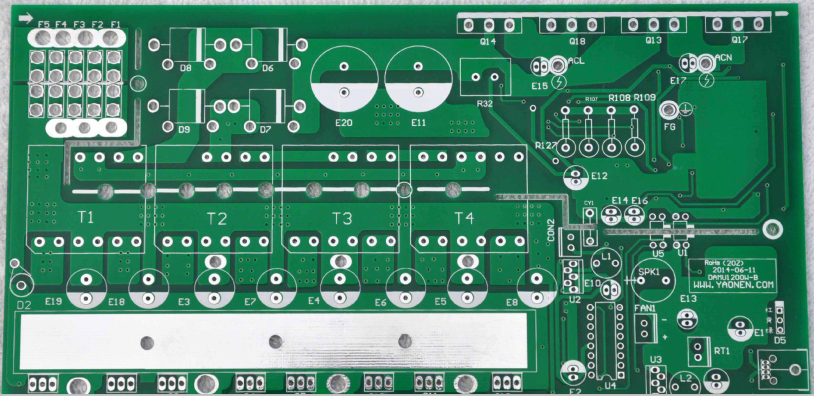

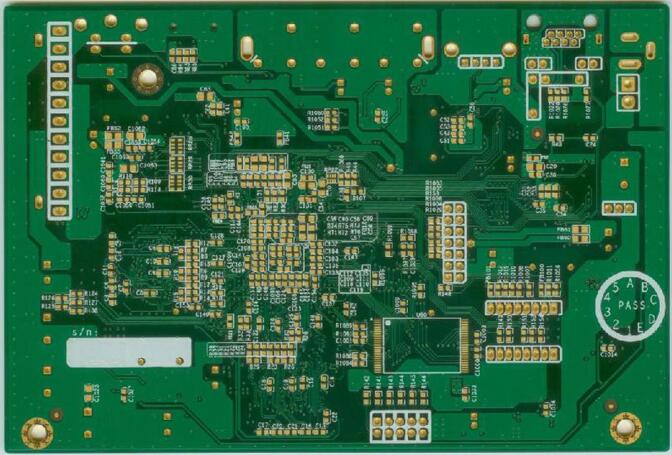

随着pcb行业迅速发展,PCB逐渐迈向高精密细线路、小孔径、高纵横比(6:1-10:1)方向发展,孔铜要求20-25Um,其中DF线距≤4MIl之板,一般生产pcb公司都存在电镀夹膜问题。下面小编来详细的说一说多层pcb打样过程中电镀夹膜产生的原因和如何改善处理。

多层pcb打样过程中电镀夹膜产生的原因

1、板件图形分布不均匀,孤立的几根线路在图形电镀过程中,因电位高,镀层超出膜厚,形成夹膜造成短路。

2、抗镀膜层太薄,电镀时因镀层超出膜厚,形成PCB夹膜,特别是线间距越小越容易造成夹膜短路。

多层pcb打样过程中电镀夹膜改善方法

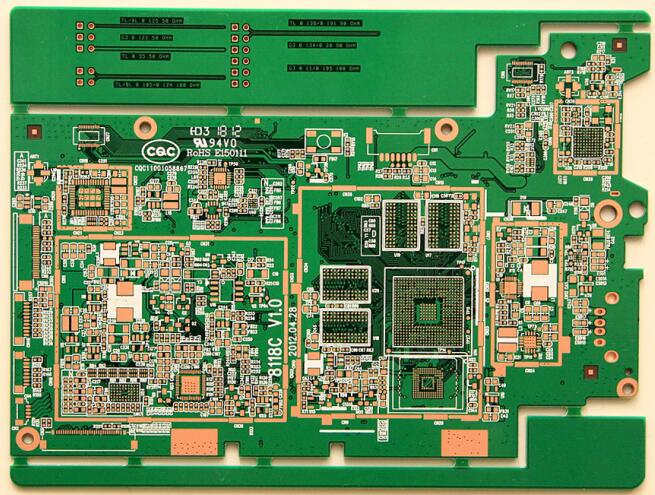

1、增加抗镀层的厚度:选择合适厚度的干膜,如果是湿膜可以用低网目数的网版印制,或者通过印制两次湿膜来增加膜厚度。

2、板件图形分布不均匀,可以适当降低电流密度(1.0~1.5A)电镀。在日常生产中,我们出于要保证产量的原因,所以我们对电镀时间的控制通常是越短越好,所以使用的电流密度一般为1.7~2.4A之间。

这样在孤立区上得到的电流密度将会是正常区域的1.5~3.0倍,往往造成孤立区域上间距小的地方镀层高度超过膜厚度很多,退膜后出现退膜不净,严重者便出现线路边缘夹住抗镀膜的现象,从而造成夹膜短路,同时会使得线路上的阻焊厚度偏薄。

以上就是小编介绍的关于多层pcb打样过程中电镀夹膜产生的原因和如何改善处理,希望对大家有所帮助,如还有不清楚的地方,请联系右侧的QQ、微信或者电话,我们会有专业的人员为您解答。

免责声明:部分文章信息来源于网络以及网友投稿,本网站只负责对文章进行整理、排版、编辑,是出于传递 更多信息之目的,并不意味着赞同其观点或证实其内容的真实性,如本站文章和转稿涉及版权等问题,请作者在及时联系本站,我们会尽快和您对接处理。

标题:多层pcb打样过程中电镀夹膜产生的原因和如何改善处理

地址:/news/686.html

本站所有内容、图片未经过私人授权,禁止进行任何形式的采集、镜像、复制,否则后果自负!

标题:多层pcb打样过程中电镀夹膜产生的原因和如何改善处理

地址:/news/686.html

本站所有内容、图片未经过私人授权,禁止进行任何形式的采集、镜像、复制,否则后果自负!

推荐资讯

- 2021-12-25PCB打样中焊盘和过孔的区别是什么

- 2021-12-25双面快速pcb打样公司哪里的服务比较好

- 2021-12-25阻抗pcb打样厂家介绍pcb蚀刻发生严重侧蚀过蚀的原因

- 2021-12-25pcb画好后怎么去打样 pcb打样怎么才能省钱

- 2021-12-25pcb打样线宽要多大 pcb打样大小

- 2021-12-25PCB打样厂家哪一家便宜

- 2021-12-25pcb打样镀金工艺上锡不良的三个原因

- 2021-12-25西安pcb打样公司:PCB与PCBA的区别在哪里

- 2021-12-25选择pcb打样厂家的注意事项

- 2021-12-25北京pcb打样价格和批量价格是多少

- 2021-12-25pcb打样厂介绍什么是线路板镀金?线路板镀金工艺介绍

- 2021-12-25PCB打样是什么意思?PCB打样需要注意哪些事项?

- 2021-12-26pcb快速打样厂家有哪些

- 2021-12-26PCB电路板打样哪家好

- 2021-12-26PCB电路板打样报价

- 2021-12-25厂家直销的24小时加急PCB打样价格是多少?

- 2021-12-25深圳24小时加急pcb打样厂家哪家好 多少钱

- 2021-12-26pcb板快打样多少钱 pcb板快打样哪家好

- 2021-12-25南昌pcb打样:单面板和双面板的区别详解

- 2021-12-25高品质的深圳PCB打样供应商推荐

新闻中心